# 集積化に向けたイオン注入によるダイヤモンド MOSFETの形成とデバイス特性評価

○上原 さくら<sup>1</sup>, 関 裕平<sup>1,2</sup>, 星野 靖<sup>2</sup>, 梅沢 仁<sup>3</sup>, 金子 純一<sup>1</sup><sup>1</sup>北海道大学, <sup>2</sup>神奈川大学, <sup>3</sup>国立研究開発法人産業技術総合研究所

## Summary

- イオン注入技術を用いて、FETのソースドレインのp<sup>+</sup>領域を形成し、水素終端ダイヤモンドMOSFETを試作

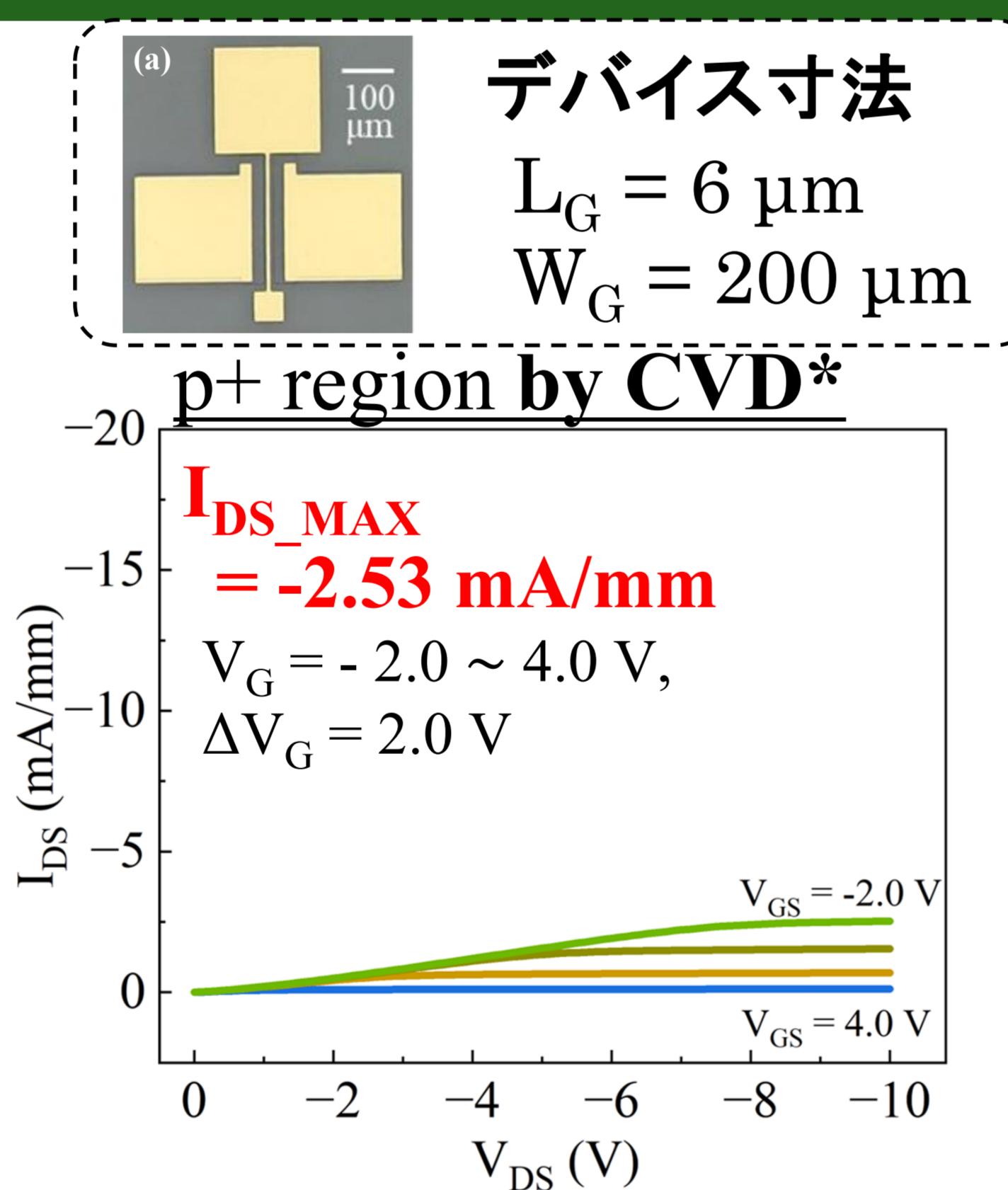

- 同一寸法、同一プロセスでCVD法を用いてp<sup>+</sup>領域を形成したMOSFETを作製し、両者の特性を定量評価

- イオン注入法で作製したデバイスはCVD法の6.6倍の出力電流密度を示した

- イオン注入法で形成した埋め込みp<sup>+</sup>電極は良好なオーミック特性を示すことを確認

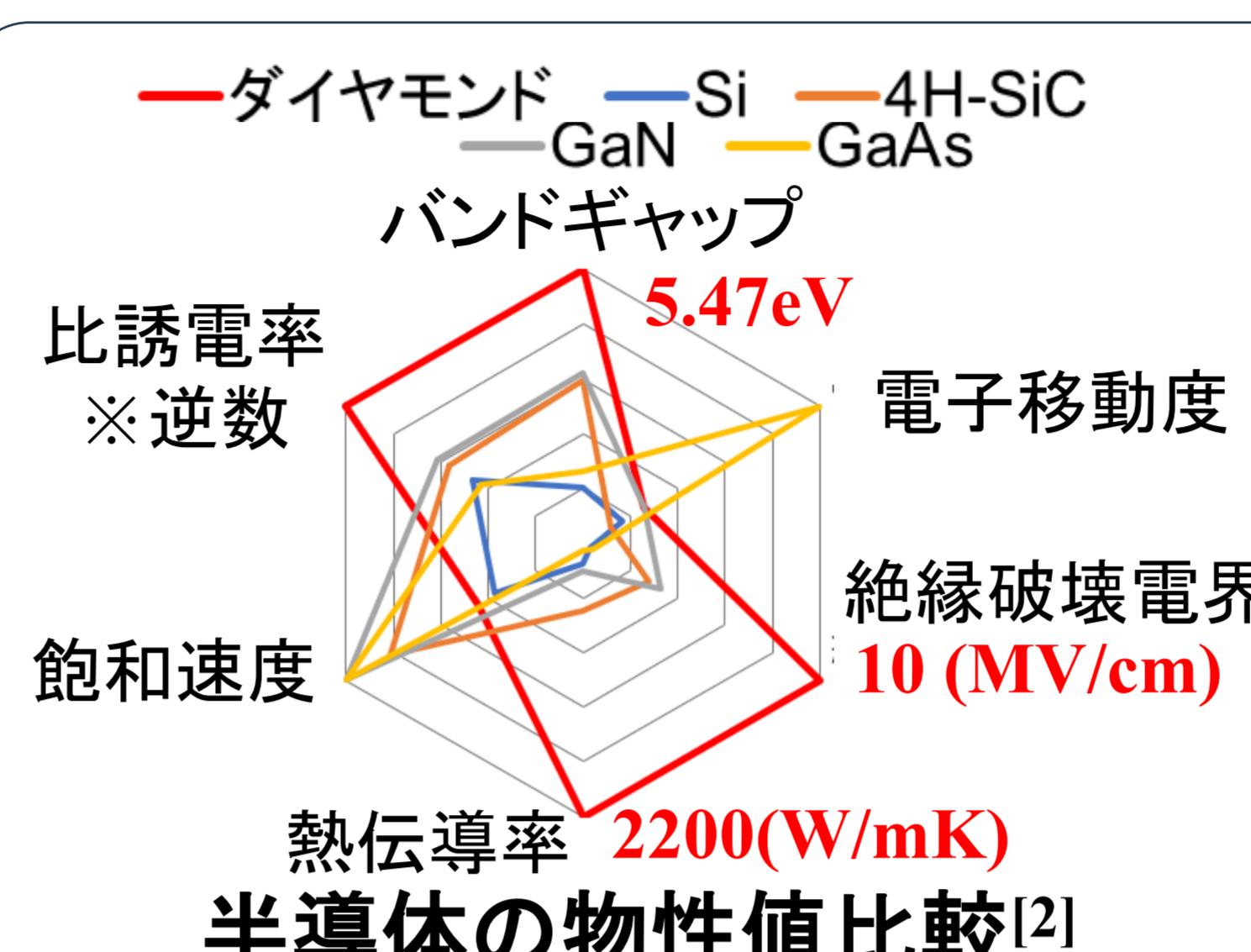

## 1. 研究背景

過酷環境で使用可能な電子機器の必要性増加

⇒ ダイヤモンド半導体デバイスの開発<sup>[1]</sup>

## 社会実装

## 耐環境用ロボット

- ・原子力

- ・火力発電所

## 通信機器

- ・6G基地局

- ・衛星通信

## デジタル集積回路

## 高周波デバイス

が必要

高集積化を前提とした

デバイスプロセスの構築 が必須

## 2. 研究目的

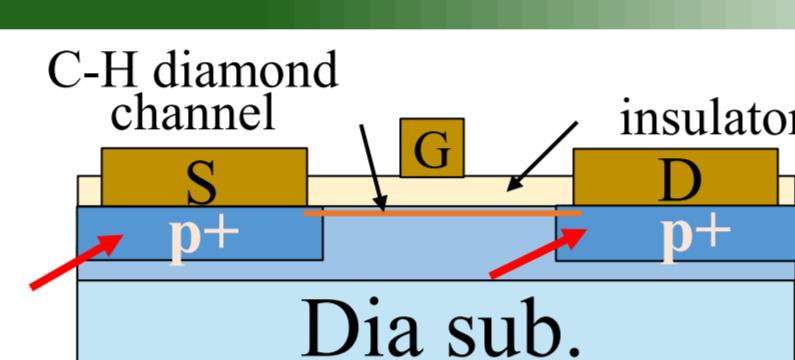

### イオン注入技術による ダイヤモンド MOSFETの埋め込みp<sup>+</sup>電極の形成

## 従来手法

化学気相成長法

- × ドーピング精度

- × 位置合わせ精度

集積化・微細化に不向き<sup>[3]</sup>

## 実現目標

★ イオン注入法<sup>[4]</sup>

- ◎ 位置精度

- ◎ 注入深さ / 濃度の制御性

集積化・微細化の要となる技術

- ソース・ドレイン電極のp<sup>+</sup>領域をイオン注入技術により形成した

水素終端ダイヤモンド MOSFET を試作

- 同一寸法・プロセスでCVD 法により p<sup>+</sup>領域を形成した

MOSFETを作製し、特性を定量比較

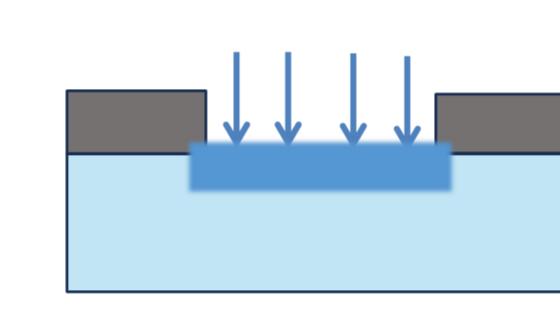

## 3. プロセス

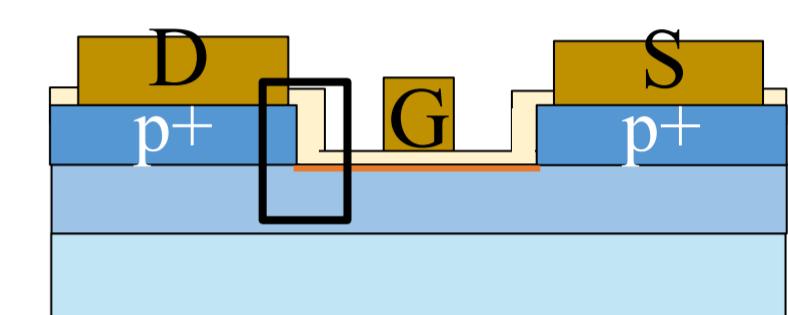

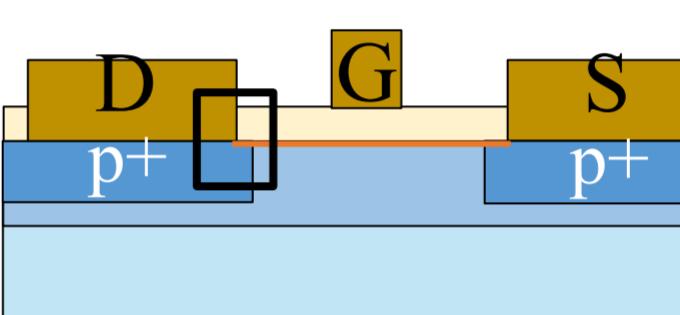

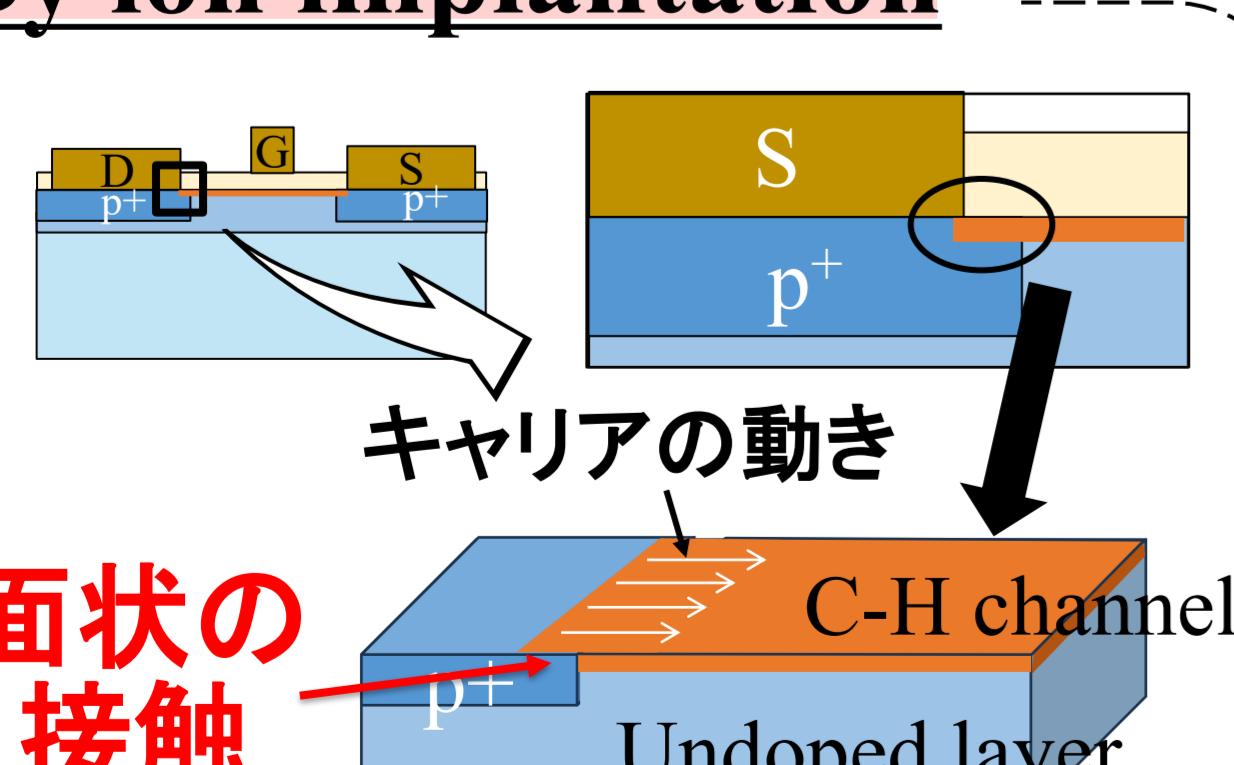

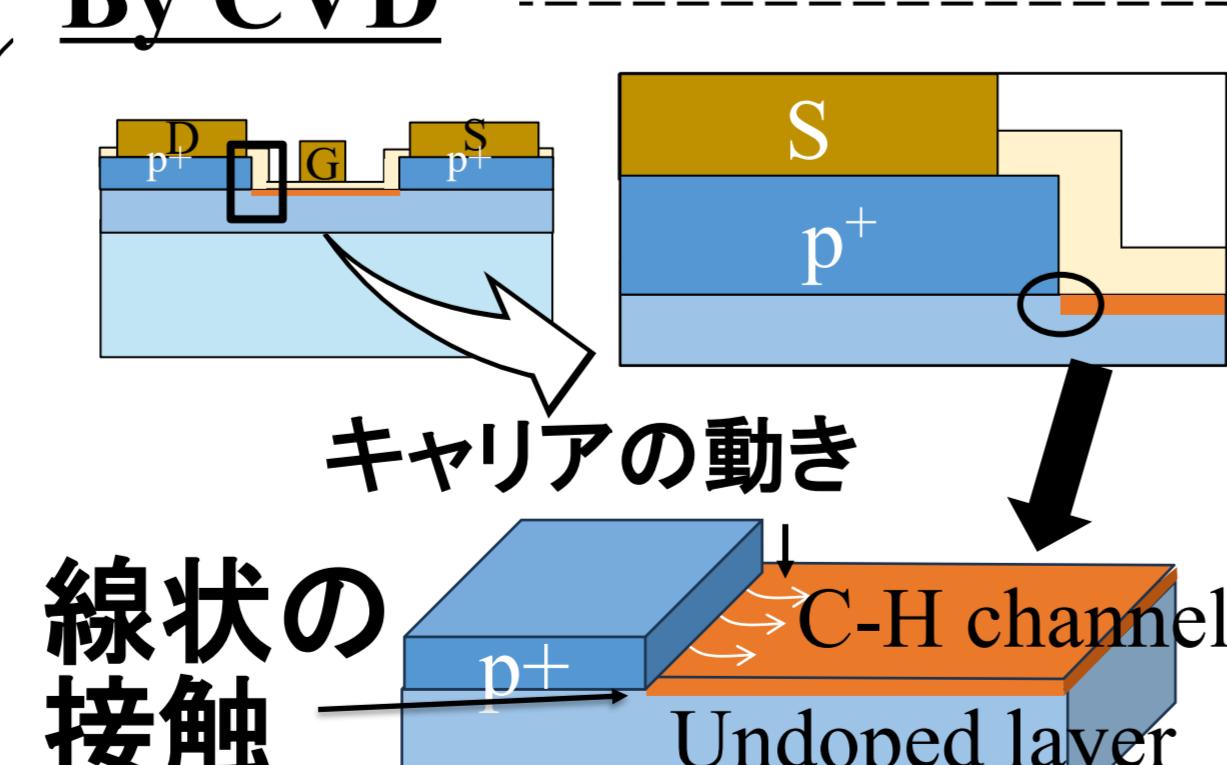

p<sup>+</sup> 形成手法のみを変えて同一寸法のMOSFETを作製

## ● ノンドープ層合成

● p<sup>+</sup>層形成

- By ion implantation

- By CVD

## ● 水素終端処理

● 絶縁膜 (Al<sub>2</sub>O<sub>3</sub>) 形成

ALD 350°C/30 nm

## ● 電極形成

Au/Pt/Ti (200/30/30 nm)

(Supattering)

★ By ion implantation

By CVD

## B イオン注入

基板温度 800 °C

20, 30, 50 keV

$4.5 \times 10^{16} \text{ cm}^{-2}$

## 選択成長

HFCVD

## ポストアニール

Ar, 1 atm 1300°C/2h

## 4. 実験結果

### トランジスタ性能の評価

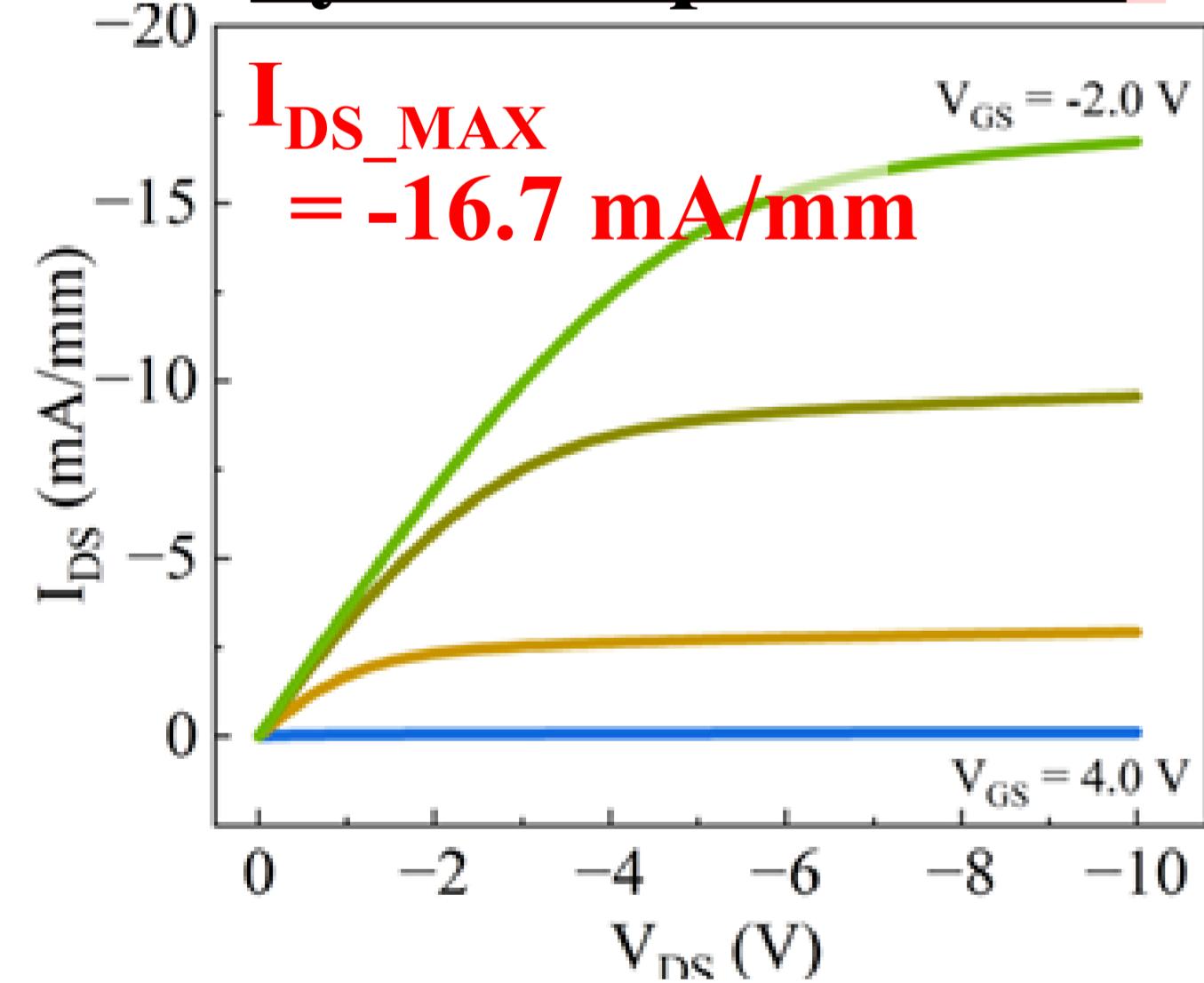

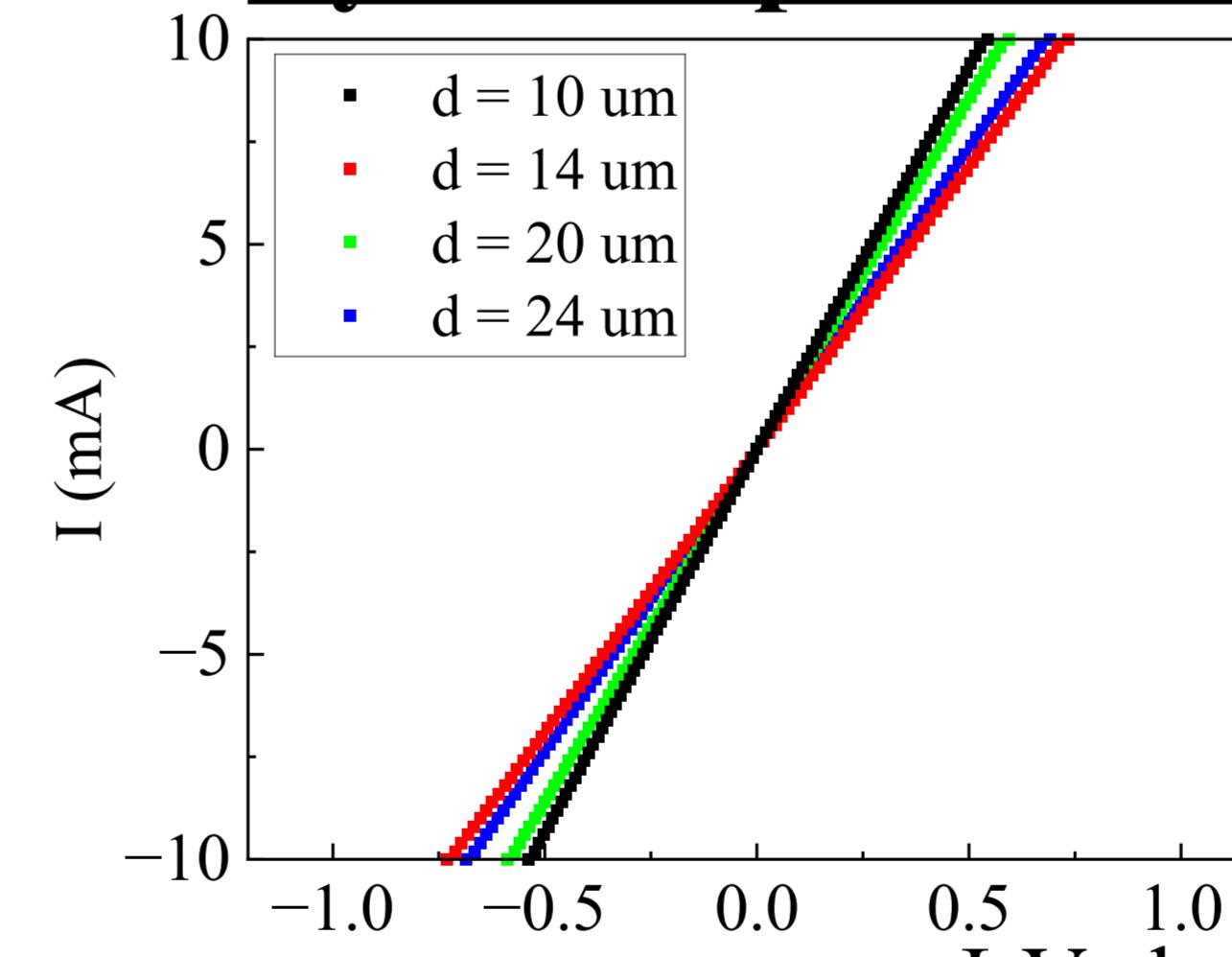

► I<sub>DS</sub>-V<sub>DS</sub> 特性の比較★ Buried p<sup>+</sup> region

by ion implantation

イオン注入法によるMOSFETの

最大ドレン電流密度  $I_{DS\_MAX}$

CVD法の約6.6倍

## ► 考察 伝導層との接觸領域の違いの比較

★ By ion implantation

面状の接觸

キャリアの動き

C-H channel

Undoped layer線状の接觸

キャリアの動き

C-H channel

Undoped layer

⇒ キャリアの移動が円滑になり、電流が流れやすくなった

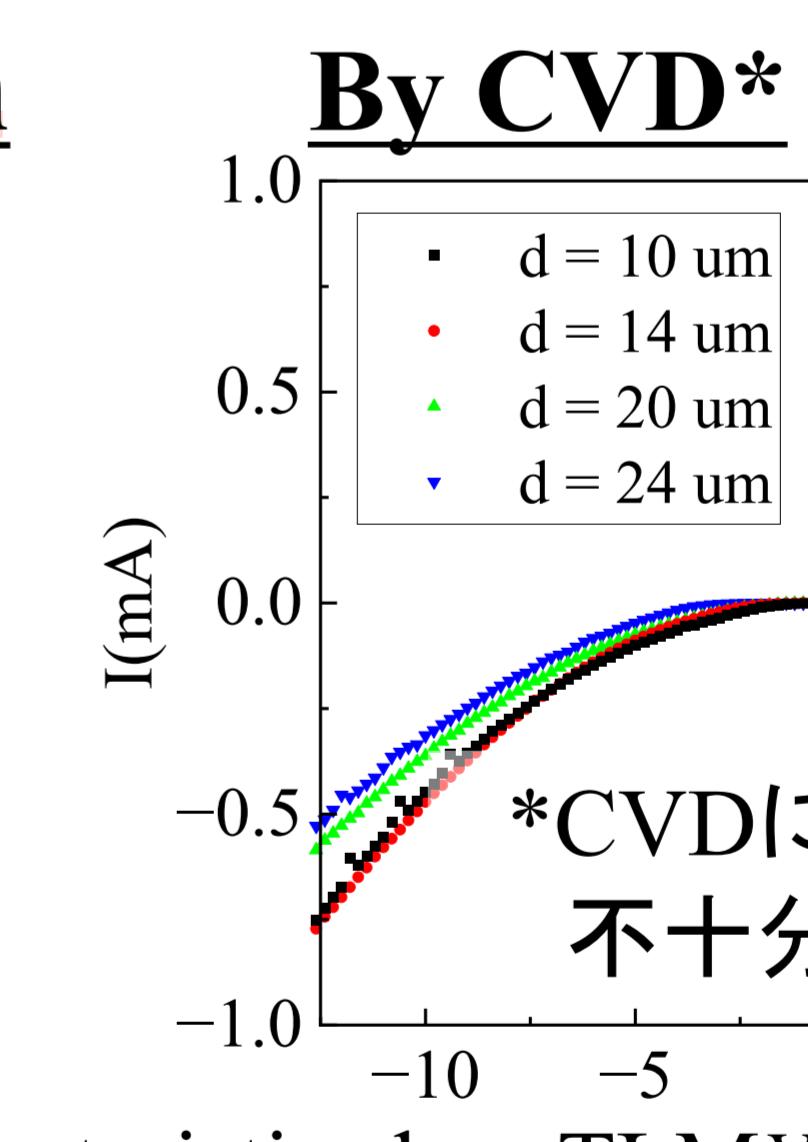

### 接触抵抗の評価

FETとは別の基板上に作製した

CTLM\* 電極の IV 特性を評価

## ► I-V 特性の比較

★ By ion implantation

イオン注入法による高濃度 B ドーピングによって

金属 / p<sup>+</sup> 間での良好なオーミック特性を実現\*CVDによるp<sup>+</sup>層のB濃度が

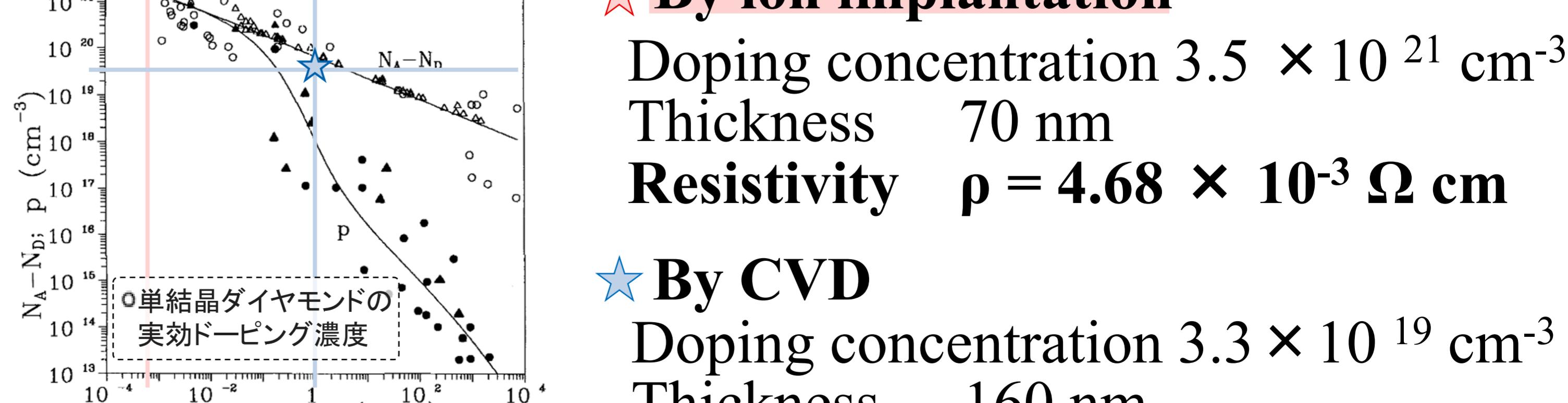

不十分だった可能性あり?► 考察 文献値との抵抗率  $\rho$  ( $\Omega \text{ cm}$ )の比較<sup>[5]</sup>

★ By ion implantation

Doping concentration  $3.5 \times 10^{21} \text{ cm}^{-3}$

Thickness 70 nm

Resistivity  $\rho = 4.68 \times 10^{-3} \Omega \text{ cm}$

★ By CVD

Doping concentration  $3.3 \times 10^{19} \text{ cm}^{-3}$

Thickness 160 nm

Resistivity  $\rho = 1.28 \Omega \text{ cm}$ \*実測値を

プロット

## 参考文献

[1] T. Yamaguchi et al., Appl. Phys. Lett. 118, 162105 (2021)

[2] 東芝デバイス&amp;ストレージ株式会社, ワイドバンドギャップ半導体とは, 2025年7月

[3] Y. Seki et al., Jpn. J. Appl. Phys. 59 021003 (2020)

[4] 獅子口清一, Materia Japan, 第38巻 第2号(1999)

[5] M. Yokoba, J. Appl. Phys. 81, 6815–6821 (1997)

[6] M. WERNER et al., phys. stat. sol. (a) 154, 385 (1996)

## 謝辞

本研究の一部は F-REI 委託研究費(JPFR25010501)、防衛装備庁

が実施する安全保障技術 研究推進制度JPJ004596の支援を受けて

実施された。